ARM处理器

ARM处理器

# ARM处理器

# 1. ARM 处理器概述

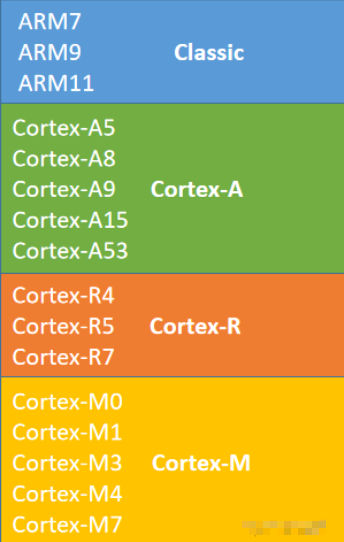

# 1.1 ARM 产品系列

早先经典处理器:包括 ARM7、ARM9、ARM11 家族

Cortex-A 系列:针对开放式操作系统的高性能处理器,应用于智能手机、数字电视、智能本等高端运用。

Cortex-R 系列:针对实时系统、满足实时性的控制需求,应于汽车制动系统、动力系统等。

Cortex-M 系列:为单片机驱动的系统提供了低成本优化方案,应用于传统的微控制器市场、智能传感器、汽车周边等。

# 1.2 RISC 处理器

RISC 处理器:

只保留常用的的简单指令,硬件结构简单,复杂操作一般通过简单指令的组合实现,一般指令长度固定,且多为单周期指令;

RISC处理器在

功耗、体积、价格等方面有很大优势,所以在嵌入式移动终端领域应用极为广泛

CISC 处理器:

不仅包含了常用指令,还包含了很多不常用的特殊指令,硬件结构复杂,指令条数较多,一般指令长度和周期都不固定;

CISC 处理器在

性能上有很大优势,多用于PC及服务器等领域。

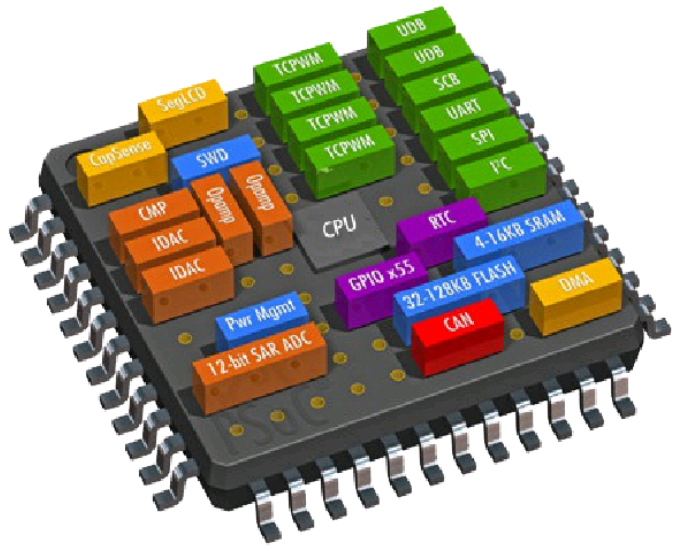

# 1.3 SOC(片上系统)

将一个系统中所需要的全部部件集成在一个芯片中在体积、功耗、价格上有很大优势

# 2. ARM 指令集

# 2.1 指令集

- 指令

能够指示处理器执行某种运算的命令称为指令(如加、减、乘 …)

指令在内存中以机器码(二进制)的方式存在

每一条指令都对应一条汇编

程序是指令的有序集合

- 指令集

处理器能识别的指令的集合称为指令集

不同架构的处理器指令集不同指令集是处理器对开发者提供的接口

# 2.2 ARM 指令集

ARM 指令集

所有指令(机器码)都占用

32bit存储空间代码灵活度高、简化了解码复杂度

执行 ARM 指令集时 PC 值

每次自增4

Thumb 指令集

所有指令(机器码)都占用

16bit存储空间代码密度高、节省存储空间

执行 Thumb 指令集时 PC 值

每次自增2

# 2.3 编译原理

机器码(二进制)是处理器能直接识别的语言,不同的机器码代表不同的运算指令,不同的处理器机器码不同,所以机器码不可移植汇编语言是机器码的符号化,即汇编就是用一个符号来代替一条机器码,所以不同的处理器汇编也不一样,即汇编语言也不可移植C语言在编译时我们可以使用不同的编译器将C源码编译成不同架构处理器的汇编,所以C语言可以移植

# 3. ARM 存储模型

# 3.1 ARM 数据类型

- ARM 采用 32 位架构,基本数据类型有以下三种:

- Byte: 8bits

- HalfWord: 16bits

- Word: 32bits

- 数据类型

- Word 型数据在内存的起始地址必须是 4 的整数倍

- HalfWord 型数据在内存的起始地址必须是 2 的整数倍

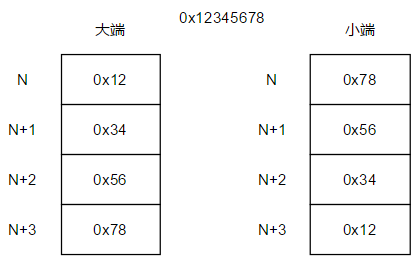

# 3.2 字节序

- 大端对齐 - 低对高:低地址存放高位,高地址存放低位

- 小端对齐 - 低对低:低地址存放低位,高地址存放高位

例如:

# 3.3 ARM 指令存储

处理器处于 ARM 状态时

所有指令在内存的起始地址必须是 4 的整数倍

PC值由其

[31:2]决定,[1:0]位未定义

处理器处于 Thumb 状态时

所有指令在内存的起始地址必须是 2 的整数倍

PC值由其

[31:1]决定,[0]位未定义

注:即指令本身是多少位在内存存储时就应该多少位对齐

# 4. ARM 工作模式

ARM 有8个基本的工作模式

User : 非特权模式,一般在执行上层的应用程序时 ARM 处于该模式

FIQ : 当一个高优先级中断产生后 ARM 将进入这种模式

IRQ : 当一个低优先级中断产生后 ARM 将进入这种模式

SVC : 当复位或执行软中断指令后 ARM 将进入这种模式

Abort : 当产生存取异常时 ARM 将进入这种模式

Undef : 当执行未定义的指令时 ARM 将进入这种模式

System : 使用和 User 模式相同寄存器集的特权模式

Monitor : 为了安全而扩展出的用于执行安全监控代码的模式

按照

权限分类User为非特权模式(权限较低),其余模式均为特权模式(权限较高)按照

状态分类FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后会进入对应的模式