NAND Flash 的 SDR、ONFI、DDR 接口

NAND Flash 的 SDR、ONFI、DDR 接口

# NAND Flash 的 SDR、ONFI、DDR 接口

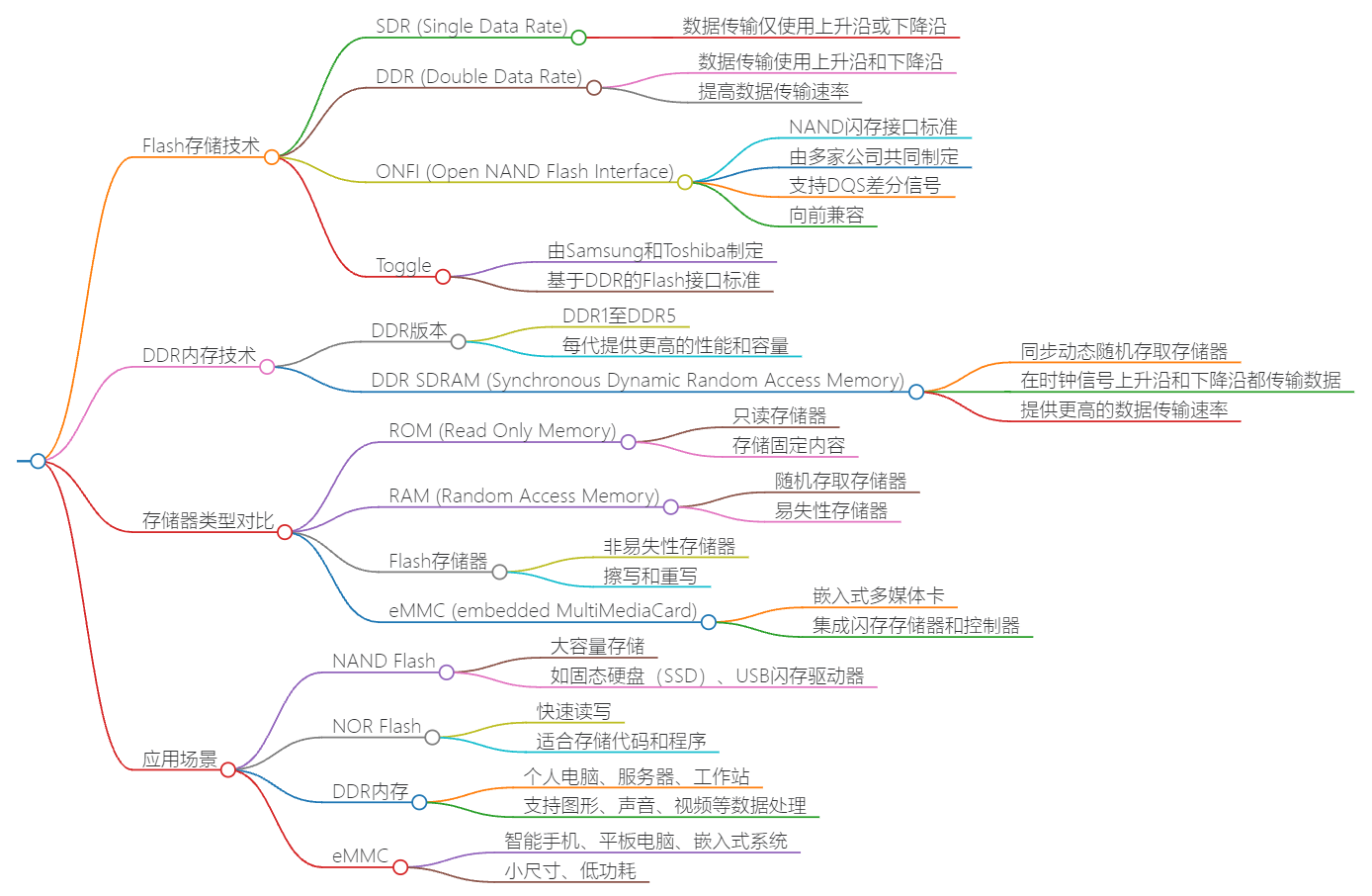

# 1. 省流导图

# 2. SDR、ONFI、DDR 概述

# 2.1 SDR (Single Data Rate)

SDR(Single Data Rate)是指读写数据使用 单个时钟信号的边缘,即上升沿或下降沿 。在 SDR 模式下,数据的传输速率受限于时钟信号的频率,因此其传输效率相对较低。

# 2.2 ONFI (Open NAND Flash Interface)

ONFI(Open NAND Flash Interface)是一个开放的 NAND Flash 接口标准,由多家存储厂商共同创建。ONFI 标准定义了 NAND Flash 的物理接口、封装、工作机制、控制指令、寄存器等规范,以实现不同厂商之间的 NAND Flash 产品的互操作性。ONFI 1.0 标准最初提供了 50MB/s 的传输带宽,随后的版本如 ONFI 2.0 和 ONFI 3.0 等逐步提高了传输速度,并增加了对 DDR 操作的支持。

# 2.3 DDR (Double Data Rate)

DDR(Double Data Rate)是一种提高数据传输速率的技术,它允许在时钟信号的 ==上升沿和下降沿都传输数据== ,从而在每个时钟周期内完成两次数据的传输。DDR 技术在 DRAM 领域中广泛应用,并被应用于 NAND Flash 接口标准中,如ONFI 2.0 中的 NV-DDR 和 Toggle 接口标准中的 DDR1 和 DDR2。

NAND Flash 存储技术中不同的数据传输速率和接口标准影响着 NAND Flash 的性能和兼容性。

# 3. SDR (Single Data Rate)

# 3.1 概述

SDR(Single Data Rate)模式是NAND Flash中的一种数据传输方式,其特点是在读写数据时仅使用时钟信号的上升沿或下降沿来触发数据传输。这种模式对信号的准确性要求较低,因此在某些应用场景下可以简化硬件设计和减少功耗。

在SDR模式下,数据的接收和发送都是通过时钟信号的特定边缘来进行的。例如,在某些应用中,当 QSPI 驱动 IO0/SO、IO1、IO2、IO3 信号时,这些信号仅在 CLK 的下降沿发生转变,并且在接收数据时也假定 Flash 通过 CLK 的下降沿发送数据。此外,对于 MXRT1010 处理器,在 SDR 模式下,Flash 会在 SCLK 的上升沿接收数据,并在 SCLK 的下降沿发送数据。

# 3.2 应用

在特定应用场景中,SDR 模式 Flash 仍然具有显著优势。以下是几个主要场景:

- 小数据-低时延应用:在需要快速处理和传输少量数据的场景中,SDR 模式 Flash 表现出色。例如,在通信系统测试、物联网设备以及雷达系统中,这些应用对时延要求较高,而SDR模式Flash能够提供快速的数据访问和处理能力。

- 大数据-高带宽需求:尽管在大数据量传输时,高带宽模式(如 DDR)可能更优,但在某些情况下,SDR 模式 Flash依然有其独特的优势。例如,在一些嵌入式系统中,由于硬件资源有限,使用 SDR 模式 Flash 可以有效减少功耗和成本。

- 异步、可扩展的运行环境:在需要灵活配置和扩展性的应用场景中,SDR模式 Flash 也显示出其优势。例如,在软件定义无线电(SDR)系统中,通过支持多种模式(包括 SDR 和 DDR),可以实现更高的灵活性和适应性。

- 高清视频播放系统:对于非高清、非超高清、SDR 的片源,通过视频综合增强技术,可以将其转化为更高清晰度的视频内容。这种应用不仅提升了观影体验,还展示了 SDR 模式 Flash 在图像处理和视频增强中的潜力。

- 空间应用中的闪存管理:在航天器等空间应用中,由于环境复杂且对可靠性要求极高,SDR 模式 Flash 因其稳定性和低功耗特性而被广泛采用。此外,通过先进的缓解策略,可以进一步提高其安全性和性能。

# 4. ONFI (Open NAND Flash Interface)

# 4.1 发展历程

ONFI (opens new window)(Open NAND Flash Interface)标准是由英特尔,镁光,海力士,台湾群联电子,SanDisk, 索尼,飞索半导体为首宣布统一制定的连接 NAND 闪存和控制芯片的接口标准,当初制定 ONFI 标准的主要目的是统一当时混乱的闪存标准。

2006年,随着手机、MP3播放器、U盘的需求量逐渐增大,以及开始步入消费市场的 SSD,市场对 NAND 闪存的需求也增加不少,而当时各个闪存制造厂所用的设计标准各有不同,这样导致闪存控制器厂商和下游产品制造厂在制作产品时碰到各种麻烦,业界迫切需求一个统一的标准,这就是ONFI的诞生背景。

ONFI 1.0 制定于2006年12月,内容主要是制定闪存的物理接口、封装、工作机制、控制指令、寄存器等规范,增加对 ECC 的支持,传输带宽从传统的 Legacy 接口的 40MB/s 提升到 50MB/s,性能提升幅度不大,不过其主要目的还是统一闪存接口规范,减轻产品厂商的开发压力。

ONFI 2.0 标准诞生于2008年2月,2.0标准将带宽速度提高到 133MB/s 以满足高速设备对闪存性能的需求,在该版本中,主要是通过两项技术来提高传输速度。第一项就是在 DRAM 领域里常用的 DDR(Double Data Rate,双倍数据率)信号技术。第二项是使用源同步时钟来精确控制锁存信号,使其能够达到更高的工作频率。

ONFI 2.1 标准于2009年1月发布,带宽提升到 166MB/s和200MB/s(工作模式不同速度不同),8KB page 数据传输延时降低,改良电源管理降低写入操作能耗,加强ECC纠错能力,新增“Small Data Move”与“Change Row Address”指令。

ONFI 2.2 发表于2009年10月,增加了 LUN(逻辑单元号)重置、增强页编程寄存器的清除和新的 ICC 测量和规范。LUN 重置和页编程寄存器清除提升了拥有多个 NAND 闪存芯片设备的处理效率,ICC 规范则简化了下游厂家的测试程序。

ONFI 2.3 在2010年8月的闪存峰会上发布,在2.2标准的基础上加入了 EZ-NAND 协议。EZ-NAND 是 Error Zero NAND 的简写,这一协议将 NAND 闪存的纠错码管理由主控芯片中转移到闪存自身,以减轻主控芯片负担。

ONFI 3.0 规范发布,接口带宽提升到 400MB/s,需求的针脚数更少让 PCB 走线更加方便,从目前披露的资料来看,ONFI 3.0 采用更短的信道、更宽的信号间距,并加入片内终止技术,使其传输带宽能够达到 400MB/s。

# 4.2 ONFI 和 Toggle

面对 ONFI 组织的攻势,占有全球 70% NAND 产能的两大闪存生产巨头三星与东芝决定携手对抗,2007年12月,三星与东芝联合通过了一项关于闪存专利技术互换授权协议,根据这项协议,三星电子和东芝在闪存规格和技术上将完全共享。

根据项协议规定,三星将允许东芝生产和制造自己旗下的 OneNAND 和 Flex-OneNAND 闪存芯片,而东芝公司则将以自己的 LBA-NAND 和 mobileLBA-NAND 闪存芯片技术作为条件与三星电子进行交换,这些闪存芯片生产技术都是三星电子和东芝的核心技术,但是新的合作协议让双方在闪存芯片制造技术实力上都取得了进一步的增强,此外他们将一同合作研发新一代闪存产品,也就是后来的 Toggle DDR NAND 闪存。

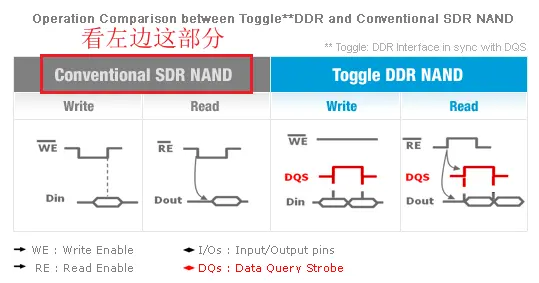

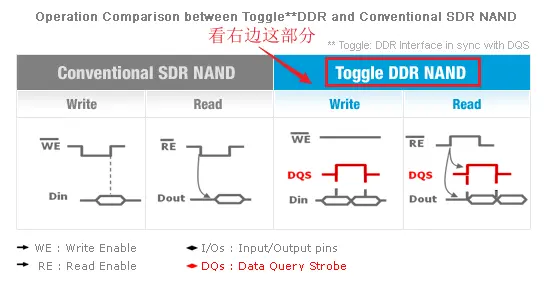

2010年6月三星与东芝开始投产符合 Toggle DDR 1.0 接口标准的 NAND 闪存,Toggle DDR NAND 采用双向 DQS 信号控制读写操作,信号的上升与下降沿都可以进行资料的传输,能使传输速度翻倍,接口带宽为 133MB/s,而且没有内置同步时钟发生器(即 NAND 还是异步设计),因此其功耗会比同步 NAND 更低。

- ONFI(Open Nand Flash Interface),由 Hynix、Inter、Micron、Phison、Sony、Spansion 于2006年共同创建的一个 Nand Flash 的接口标准,并于当年发布了 ONFI1.0 标准,支持 SDR。ONFI2.0 时增加 NV-DDR,支持 DDR 操作,不过是使用同步时钟来控制的。ONFI3.0 时,增加 NV-DDR2,ONFI4.0 时增加了 NV-DDR3。NV-DDR2 和 NV-DDR3 都是支持 DQS 差分信号而不用同步时钟的。并且 ONFI 接口都是同步向前兼容的。但是接口间的转换只支持如下几种:

- SDR to NV-DDR

- SDR to NV-DDR2

- NV-DDR to SDR

- NV-DDR2 to SDR

- Toggle,是 Samsung 和 Toshiba 以 DDR 为基础制定的 Flash 接口标准,是为了对抗 ONFI 的标准。Toggle1.0 对应 DDR1,Toggle2.0 对应 DDR2。Toggle 接口的 Flash一般也支持切换到 Legacy 接口(即 SDR,和 ONFI1.0 是相同的)。Toggle 接口 Flash 一般启动时是 Legacy Mode,需要设置才能进入Toggle Mode(DDR1/DDR2),同样在 Toggle 模式下也可以设置命令序列进入Legacy Mode(SDR)。

- 除了 ONFI2.0 时的 NV-DDR1 是需要同步时钟外,其他接口下都是 Async 模式。所以我们常说从 DDR 模式切换到 Async 模式是不太准确的说法。应该说切换到 Legacy Async、Traditinal Async 或是 SDR 模式。

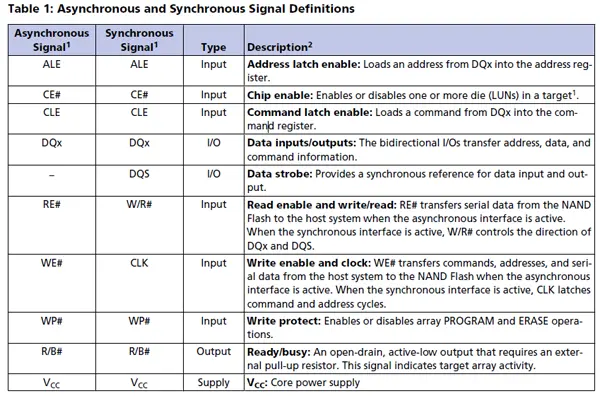

# Sync 和 Async

- Sync 模式是指 Flash 操作时需要一个源时钟来对锁存信号进行同步,提高信号采集的准确性。因为另外一个源时钟信号来进行同步,所以对 Flash 的品质要求较高,如果信号不稳定,很容易导致源时钟信号与锁存信息不对应,导致数据采样不准确。Sync 模式的 Flash一般支持 Async,当品质不达标时,便采用 Async 模式操作。

- Async,即不需要时钟信号来进行同步,数据通过 WEN/REN 来锁存。在未使用 DDR 的时候,Async 方式的操作效率是比 Sync 效率低。因为 Sync 模式有时钟同步,信号较准确,所以可以提高采样率。Async 模式为了提高效率,所以必须采用某种方式提升信号准确性。这 个时候,采用了差分信号,大幅提升了信号的准确性,为此采用了 DDR 模式采样数据。

# 4.3 闪存的同步与异步

我们经常说闪存的同步与异步模式,其实是在 ONFI 2.0 标准中新加入的特性(ToggleDDR 不存在同步闪存的情况,均为异步设计,但性能仍然强悍),ONFI 2.0 标准在 NAND 中加入了同步时钟发生器,主控可以通过发送同步指令激活闪存上的同步时钟信号,使闪存工作在同步模式 ,此时闪存的数据传输速率会大幅度提升,异步模式相当于 ONFI 1.0,闪存的带宽为 50MB/s,而同步模式下闪存至少也符合 ONFI 2.0,闪存带宽可达到 133MB/s 以上。

实际上同步与异步闪存都是同一生产线上下来的,颗粒品质的优劣才产生了这样的区别。比如英特尔 29F64G08AAME1 颗粒属于异步闪存,而英特尔 29F32B08JCME2 则支持同步/异步模式,又如镁光的 29F64G08CBAAA 是异步闪存,而 29F64G08CBAAB 颗粒支持同步/异步模式。

下面是镁光NAND在异步与同步模式下的部分针脚定义:

开机时 SSD 是运行在异步模式的,只有当主控发送同步指令给闪存后,才激活闪存上的源同步时钟,然后针脚定义发生改变,激活 DQS 信号, 让其工作在同步模式,并将异步模式下的 WE# 信号变为 CLK 信号,RE# 变为 W/R 信号,同步模式下 DQS 信号的上升沿与下级沿都能控制信号的传输,使传输速度翻倍。

市面上有少数 SSD 使用异步闪存,但强制运行在同步模式,性能是上来了,稳定性存在隐患。

# 4.4 ONFI 标准是如何确保不同厂商 NAND Flash 产品的互操作性的?

要包括以下几点:

- 标准化的通信接口规范:ONFI 定义了 NAND Flash 存储器和控制器之间的通信接口规范,包括电气接口、命令集、数据传输模式和时序参数等,这些规范保证了不同厂商的 NAND Flash 产品能够使用统一的通信方式。

- 参数页的使用:ONFI 规范中的参数页包含了关于芯片组织、功能、时序和其他行为参数的数据结构。这些信息通常存储在设备的特定区域,并可以被控制器读取,以便进行兼容性设计和驱动代码的编写。

- 自描述的特性:ONFI 标准的设备功能和特性在参数页中自我描述,这意味着控制器不需要内置硬编解码器芯片 ID表,即可识别和支持新的 NAND 设备。

- 兼容性设计:由于 ONFI 标准的互操作性设计,主机系统可以设计成支持一系列 ONFI 规范的 NAND Flash 设备,而无需为每种新设备进行专门的适配。

- 高速数据传输模式:ONFI 标准定义了与现有 NAND 闪存接口兼容的高速 NAND 接口,允许数据在控制器和 NAND Flash 之间以更高的速率传输,从而提高了整体系统的性能。

通过这些机制,ONFI 标准大大简化了 NAND Flash 的集成过程,降低了设计和开发的复杂性,同时确保了不同厂商生产的 NAND Flash 产品之间的广泛兼容性和互操作性。

# 5. DDR (Double Data Rate)

# 5.1 概述

DDR(Double Data Rate)模式是一种用于提高数据传输速率的技术。在双倍数据速率(DDR)模式下,数据可以在每个时钟周期的上升沿和下降沿各传输一次,从而实现数据传输速度的加倍。

写数据时通过 MCU 来控制 DQS 信号跳变沿来触发(即上升沿和下降沿均触发),所以对信号的准确性要求较高,(同步)可以通过增加同步时钟信号来提高信号的准确性,如 ONFI2.0 时的 DDR 就是使用此方式。(异步)另外还可以通过差分信号来提高信号准确性,Toggle 下的 DDR,ONFI3.0/ONFI4.0 下的 DDR 也都支持 DQS 差分信号 (DQS_t,DQS_c) 来进行 DDR 操作。

此外,Toggle DDR 是一种特殊的Flash存储器接口,它通过双向 DQS(Data Strobe Signal)支持双倍数据速率的操作,而不需要额外的时钟信号。这种接口不仅兼容传统 SDR Flash 存储器的功能和命令,还能提供更高的数据传输速率,并且由于分离了 DQ 电压,因此能够节省电力。

# 5.2 应用

在高性能计算和大数据处理等应用场景中,Flash DDR 技术的实际应用案例包括以下几个方面:

- 视频处理:基于 PCIe 光纤加速计算卡的 Flash DDR 技术可以用于视频处理。这种加速卡能够显著提高视频数据的处理速度,从而提升整体性能。

- 机器学习:Flash DDR 技术在机器学习领域也有广泛应用。由于其高速的数据传输能力,Flash DDR 能够支持复杂的机器学习算法和模型训练,从而加快计算过程。

- 网络加速:Flash DDR 技术还可以应用于网络加速场景。通过提供高速的数据传输能力,Flash DDR 能够优化网络通信,减少延迟,提高网络的整体效率。

- 动态随机存取存储器(DRAM)的改进:在高性能计算和大数据处理中,DRAM 是核心组件之一。Flash DDR 技术通过提高 DRAM 的密度和速度,能够有效缓解 CPU 与内存之间的数据瓶颈问题,从而提升系统的整体性能。

# 5.3 发展历程

- 早期阶段:

- 闪存技术在1980年代开始发展,最初主要使用 NOR Flash。这种类型的闪存设备常用于计算机内存中。

- NAND Flash 的崛起:

- 随着时间的推移,Flash 技术逐步取代了传统的 NAND 和 NOR Flash,成为一种更快、更可靠且成本较低的存储介质。

- NAND Flash 在1990年代末被创造出来,并迅速成为主流存储技术之一。其具有更高的读写速度和更好的持久性,广泛应用于服务器和其他需要高速数据处理的电子系统中。

- 多层结构和三维堆叠:

- 为了克服物理限制并提高容量和性能,NAND Flash 采用了多层结构和三维堆叠技术。例如,Samsung 推出了280层1Tb 4b/cell NAND,而 Micron 则推出了1Tb 3.6GT/s 3b/cell NAND。

- 制程工艺的进步:

- 制程工艺的改进也推动了 Flash 技术的发展。早期产品的更新周期大约为3到5年,但在进入20nm以内制程后,更新速度有所放缓。业界通常使用1X、1Y、1Z等术语来表达这些制程。