第6章 FTL 综述

第6章 FTL 综述

# 第6章 SSD 核心技术:FTL

# 6.1 FTL 综述

FTL (Flash Translation Layer,闪存转换层)用于完成主机逻辑地址空间到闪存物理地址空间的翻译(Translation),或者说映射(Mapping)。

SSD 将用户逻辑数据写入闪存地址空间,记录该逻辑地址到物理地址的映射关系。当主机读取该数据时,SSD 便根据映射,从闪存读取数据返回给用户。完成逻辑地址空间到物理地址空间的映射,这是 FTL 最原始且基本的功能。

FTL 除了完成基本的地址映射,还需要处理垃圾回收(GC)、磨损平衡(WearLeveling)、坏块管理、读干扰(ReadDisturb)处理、数据保持(DataRetention)处理等事情。

SSD 的存储介质除了 Flash,还有 RAM、3D XPoint 等新型存储介质。如无特别说明,后文说的 SSD 存储介质都是指 NAND Flash,翻译为 NAND 闪存,简称闪存。

闪存的一些重要特性:

- 闪存块(Block)需先擦除才能写入,不能覆盖写(out-of0place update)。

- 闪存块都是有一定寿命的,可以用 PE(Program/EraseCount,编程/擦除次数)衡量。

- 存在读干扰(Read Disturb)问题。

- 存在数据保持(Data Retention)问题。

- 闪存天生就有坏块。另外,随着 SSD 的使用,也会产生新的坏块。坏块的症状是擦写失败或者读失败(ECC 不能纠正数据错误)。坏块管理也是 FTL 的一大任务。

- QLC 或者 TLC 可以配成 SLC 模式来使用。

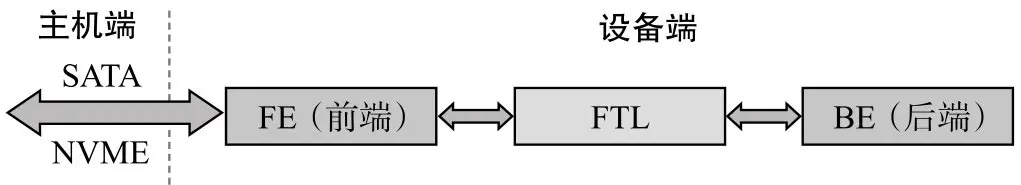

FTL 分为 Host Based(基于主机)和 Device Based(基于设备)。

- Host Based 表示的是,FTL 是在 Host(主机)端实现的,用的是你自己计算机的 CPU 和内存资源,如图4-1所示。

- Device Based 表示的是,FTL 是在 Device(设备)端实现的,用的是 SSD 上的控制器和 RAM 资源,如 图4-2 所示。

# 6.2 映射管理

# 6.2.1 映射种类

根据映射粒度的不同,FTL 映射有基于块的映射,基于页的映射,还有混合映射(Hybrid Mapping)。

# 6.2.1.1 块映射

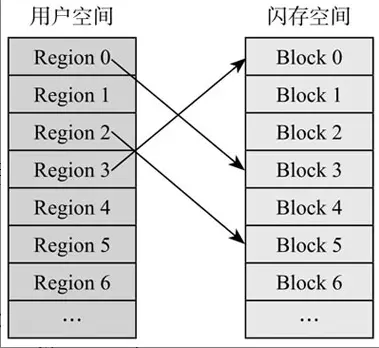

块映射,以闪存的块为映射粒度,一个用户逻辑块可以映射到任意一个闪存物理块,映射前后,每个页在块中的偏移保持不变。

- 缺点:存储映射表所需空间小,但其性能差,尤其是小尺寸数据的写入性能,用户即使只写入一个逻辑页,也需要把整个物理块数据先读出来,然后改变那个逻辑页的数据,最后再整个块写入。

- 优点:块映射有好的连续大尺寸的读写性能,但小尺寸数据的写性能是非常糟糕的。

图4-3中,用户空间被划分成一个个逻辑区域(Region),每个区域和闪存块大小相同。

U 盘一般都是采用块映射(U盘使用的存储介质也是闪存,因此也是有 FTL 的),适合大数据的传输,不适合小尺寸数据的写入。所以请不要抱怨 U 盘随机性能,装系统还是选择 SSD 吧。

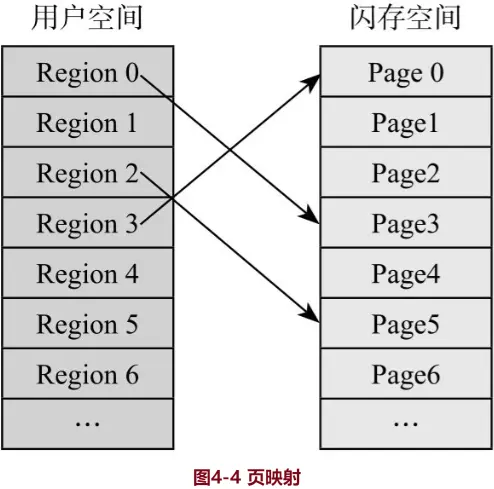

# 6.2.1.2 页映射

页映射,以闪存的页为映射粒度,一个逻辑页可以映射到任意一个物理页中,每一个页都有一个对应的映射关系,如 图4-4 所示。

- 缺点:由于闪存页远比闪存块多,因此需要更多的空间来存储映射表。

- 优点:性能更好,尤其体现在随机写上面。为追求性能,SSD 一般都采用页映射。

图4-4 中,用户空间被划分成一个个的逻辑区域,每个区域和闪存页大小相同。

实际中逻辑区域大小可能小于闪存页大小,一个闪存页可容纳若干个逻辑区域数据。

# 6.2.1.3 混合映射

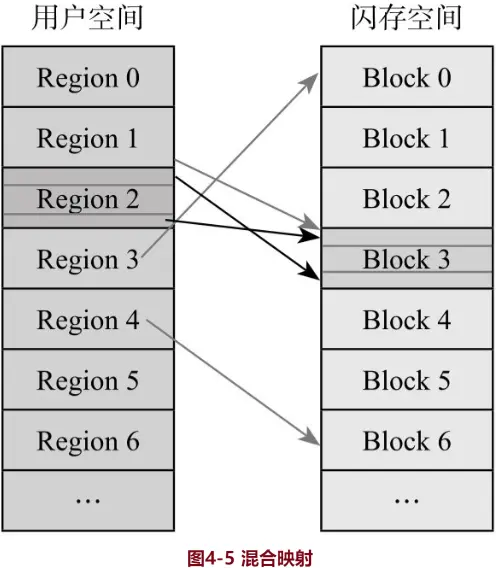

混合映射是块映射和页映射的结合,如 图4-5 所示。一个逻辑块映射到任意一个物理块,但在块中,每个页的偏移并不是固定不动的,块内采用页映射的方式,一个逻辑块中的逻辑页可以映射到对应物理块中的任意页。因此,它的映射表所需空间以及性能都是介于块映射和页映射之间的。

图4-5中,用户空间划分成一个一个逻辑区域,逻辑区域和闪存块大小相同。每个逻辑块对应着一个闪存块,但逻辑块内部又分成一个个逻辑页,与对应闪存块中的闪存页随意对应。下面对块映射、页映射和混合映射进行了对比,如表4-1所示。

表4-1 不同映射之间的比较

| 块映射 | 页映射 | 混合映射 | |

|---|---|---|---|

| 映射单元 | 物理块 | 物理页 | 块页结合 |

| 顺序写性能 | 好 | 好 | 好 |

| 顺序读性能 | 好 | 好 | 好 |

| 随机写性能 | 很差 | 好 | 差 |

| 随机读性能 | 好 | 好 | 好 |

| 映射表大小 | 小 | 大 | 一般 |

现在 SSD 基本都是采用这种映射方式。

# 6.2.2 映射基本原理

用户通过 LBA(Logical Block Address,逻辑块地址)访问 SSD,每个 LBA 代表着一个逻辑块(大小一般为512B/4KB/8KB……),用户访问 SSD 的基本单元称为逻辑页(Logical Page)。

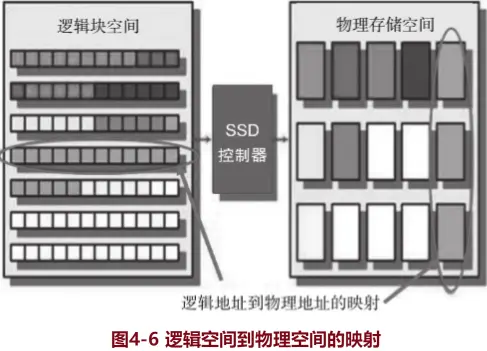

在 SSD 内部,SSD 主控是以闪存页为基本单元读写闪存的,称闪存页为物理页(Physical Page)。用户每写入一个数据页,SSD 主控就会找一个物理页把用户数据写入,SSD 内部同时记录了这样一条映射(Map)。有了这样一个映射关系后,下次用户需要读某个逻辑页时,SSD 就知道从闪存的哪个位置把数据读取上来,如 图4-6 所示。

SSD 内部维护了一张逻辑页到物理页地址转换(Logical address To Physical address, L2P)的映射表(Map Table)。用户每写入一个逻辑页,就会产生一个新的映射关系,这个映射关系会加入(第一次写)或者更改(覆盖写)映射表。当读取某个逻辑页时,SSD 首先查找映射表中该逻辑页对应的物理页,然后再访问闪存读取相应的用户数据。

由于闪存页和逻辑页大小不同,一般前者大于后者,所以实际上不会是一个逻辑页对应一个物理页,而是若干个逻辑页写在一个物理页中,逻辑页其实是和子物理页一一对应的。

# 6.2.2.1 计算映射表大小

一般来说,映射表大小为 SSD 容量大小的千分之一。准确来说,映射表大小是 SSD 容量大小的 1/1024。前提条件是:映射页大小为 4KB,物理地址用 4Byte 表示。这里假设了 SSD 内部映射粒度等于逻辑页大小,当然它们可以不一样。

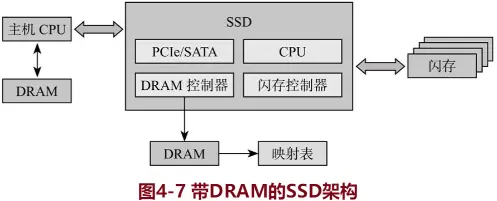

这里假设我们有一个 256GB 的 SSD,以 4KB 大小的逻辑页为例,那么用户空间一共有 64M(256GB/4KB)个逻辑页,也就意味着 SSD 需要有能容纳 64M 条映射关系的映射表。映射表中的每个单元(entry)存储的就是物理地址(PhysicalPage Address),假设其为4字节(32 bits),那么整个映射表的大小为 64M×4B = 256MB。

对于绝大多数 SSD,我们可以看到上面都有板载 DRAM,其主要作用就是存储这张映射表,如 图4-7 所示。在 SSD 工作时,全部或绝大部分的映射表都可以放在 DRAM 上,映射关系可以快速访问。

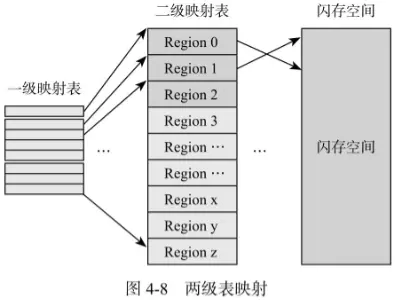

入门级 SSD 或者移动存储设备(比如 eMMC、UFS),出于成本和功耗考虑,它们采用 DRAM-Less 设计,即不带 DRAM,比如经典的 Sandforce 主控,它并不支持板载 DRAM,它采用二级映射(见 图4-8)。一级映射表常驻 SRAM,二级映射表小部分缓存在 SRAM,大部分都存放在闪存上。

二级表就是 L2P(Logical address To Physical address,逻辑地址到物理地址转换)表,它被分成一块一块(Region)的,大部分存储在闪存中,小部分缓存在 RAM 中。一级表则存储这些块在闪存中的物理地址,由于它不是很大,一般都可以完全放在 RAM 中。

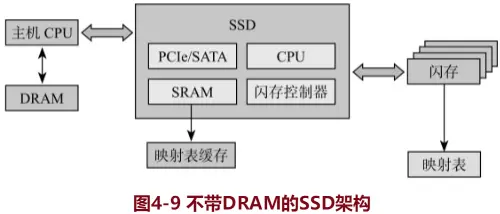

SSD 工作时,对带 DRAM 的 SSD 来说,只需要查找 DRAM 当中的映射表,获取到物理地址后访问闪存便会得到用户数据,这期间只需要访问一次闪存。而对不带 DRAM 的 SSD 来说,它首先会查看该逻辑页对应的映射关系是否在 SRAM内:如果在,直接根据映射关系读取闪存;如果不在,那么它首先需要把映射关系从闪存中读取出来,然后再根据这个映射关系读取用户数据,这就意味着相比于有 DRAM 的 SSD,它需要读取两次闪存才能把用户数据读取出来,底层有效带宽减小,如图4-9所示。

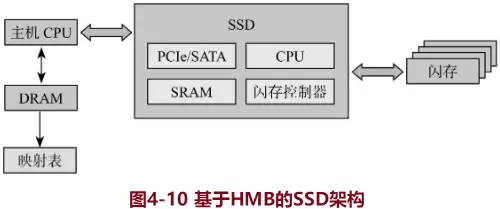

# 6.2.3 HMB

映射表除了可以放在板载 DRAM、SRAM 和闪存中,它还可以放到主机的内存中。NVME1.2(及后续版本)有个重要的功能就是 HMB(Host MemoryBuffer,主机高速缓冲存储器):主机在内存中专门划出一部分空间给 SSD 用,SSD 可以把它当成自己的 DRAM 使用。因此,映射表完全可以放到主机端的内存中去,如图4-10所示。

在性能上,它应该介于带 DRAM 和不带 DRAM(映射表绝大多数存放在闪存)之间,因为 SSD 访问主机端 DRAM 的速度肯定比访问 SSD 端 DRAM 的速度要慢,但还是比访问闪存的速度(约40μs)要快。HMB功能允许主控像使用SSD上的 DRAM 一样使用主机 DRAM。具体说来,就是主机在主存中专门划出一块内存给 SSD 使用,该内存在物理上可以不连续,SSD 不仅可以用它来存放映射表,还可以用它来缓存用户数据,具体怎么用,取决于 SSD 设计者。

如前所述,SSD 有两种设计:

一种是带 DRAM 的,DRAM 用于缓存数据和存放映射表,目前主流 SSD 都是带 DRAM 的;带 DRAM 的 SSD 设计,其优势是性能好,映射表完全可以放在 DRAM 上,查找和更新迅速;劣势就是由于增加了一个 DRAM,提高了 SSD 的成本,也加大了 SSD 的功耗。

还有一种就是不带 DRAM(DRAM-Less)的,缓存数据用主控上的 SRAM,映射表采用两级映射——一级映射和少量的二级映射放 SRAM,二级映射数据大多数存放在闪存上,这种 DRAM-Less 设计多为入门级 SSD 使用。DRAM-Less 的 SSD 设计则正好相反,优势是成本和功耗相对低,缺点是性能差。由于映射表绝大多数存储在闪存中,对随机读来说,每次读用户数据,需要访问两次闪存,第一次是获取映射表,然后才是真正读取用户数据。

# 6.2.4 映射表刷新

映射表在SSD掉电前,是需要把它写入到闪存中去的。下次上电初始化时,需要把它从闪存中部分或全部加载到SSD的缓存(DRAM或者SRAM)中。随着SSD的写入,会不断增加新的映射关系,为防止异常掉电导致这些新的映射关系丢失,SSD的固件不仅仅只在正常掉电前把这些映射关系刷新到闪存中去,而是在SSD运行过程中,按照一定策略把映射表写进闪存。这样,即使发生异常掉电,丢失的也只是一小部分映射关系,上电时可以较快地重建这些映射关系。

一般有以下几种情况触发映射表写入:

- 新产生的映射关系累积到一定的阈值

- 用户写入的数据量达到一定的阈值

- 闪存写完闪存块的数量达到一定的阈值

写入策略:

- 全部更新:全部更新表示的是缓存中映射表(干净的和不干净的)全部写入到闪存

- 增量更新:增量更新的意思是只把新产生的(不干净的)映射关系刷入到闪存中去

# 6.3 垃圾回收

# 6.3.1 垃圾回收原理

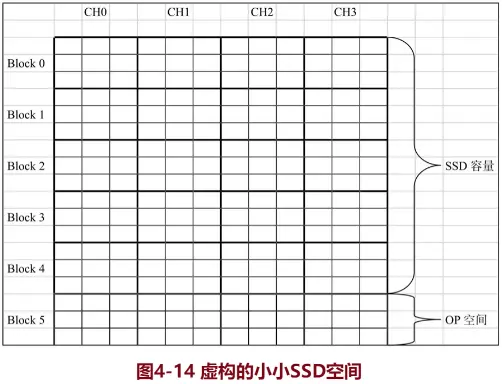

我们假设该 SSD 底层有4个通道(CH0~CH3),连接着4个Die(每个通道上的 Die 可并行操作),假设每个 Die 只有6个闪存块(Block0~Block5),所以一共24个闪存块。每个闪存块内有9个小方块,每个小方块的大小和逻辑页大小一样。24个闪存块中,我们假设其中的20个闪存块大小为 SSD 容量,就是主机端看到的 SSD 大小;另外4个闪存块是超出 SSD 容量的预留空间,我们称之为 OP,如 图4-14所示。

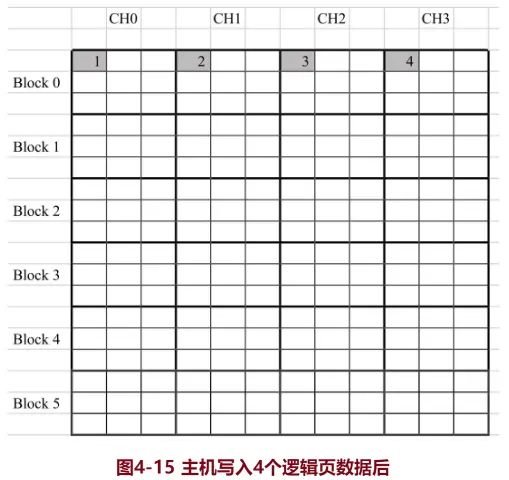

我们顺序写入4个逻辑页,分别写到不同通道的 Die 上,这样写的目的是增加底层的并行性,提升写入性能,如图4-15所示。

我们继续顺序写入,固件则把数据交错写入到各个 Die 上,直到写满整个 SSD 空间(主机端看到的)如图4-16所示。

整个盘写满了(从用户角度来看也就是整个用户空间写满了,但在闪存空间,由于 OP(OverProvisioning,预留空间) 的存在,并没有写满)。那如果想写入更多,只能把看过的内容删除了,腾出空间放新的内容。

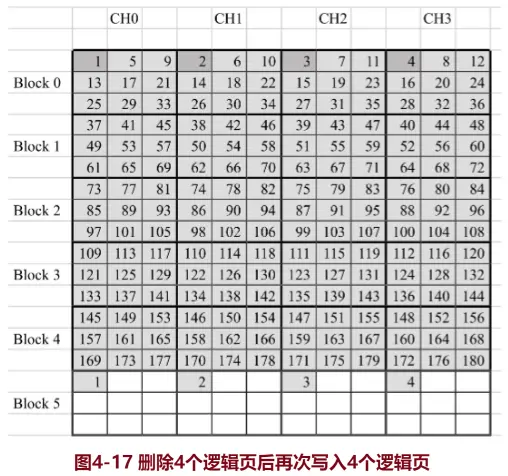

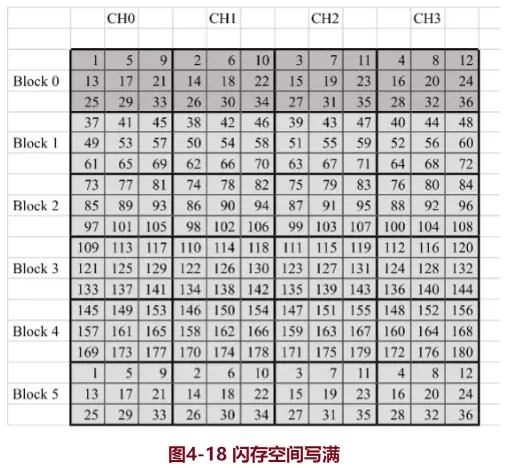

下面我们继续拷入。假设还是从逻辑页1开始写入。这时,SSD 会把新写入的逻辑页写入到所谓的 OP 空间。对 SSD 来说,不存在什么用户空间和 OP 空间,它只会看到闪存空间。主机端来数据,SSD 就往闪存空间写。图4-17 中出现了深色方块,怎么回事?因为逻辑页1~4的数据已更新,写到新的地方,那么之前那个位置上的逻辑页1~4数据就失效了,过期了,变垃圾了。用户更新数据,由于闪存不能在原位置覆盖写,固件只能另找闪存空间写入新的数据,因此导致原闪存空间数据过期,形成垃圾。

继续顺序写入,深色方块越来越多(垃圾数据越来越多)。所有闪存空间都写满后,小 SSD 就是下面这个样子(见图4-18)。

等所有 Die 上的 Block 5 写满后,所有 Die 上的 Block 0 也全部变色了(这些数据都是垃圾)。现在不仅整个用户空间都写满,整个闪存空间也都满了。如果用户想继续写入后续的逻辑页(36之后的),该怎么办呢?

这时,就需要垃圾回收了。我们暂时从之前的SSD系统中走出来,看看什么是垃圾回收。

需要说明的是,实际中是不会等所有闪存空间都写满后才开始做GC的,而是在满之前就触发GC,这里只是为描述GC而做的假设。

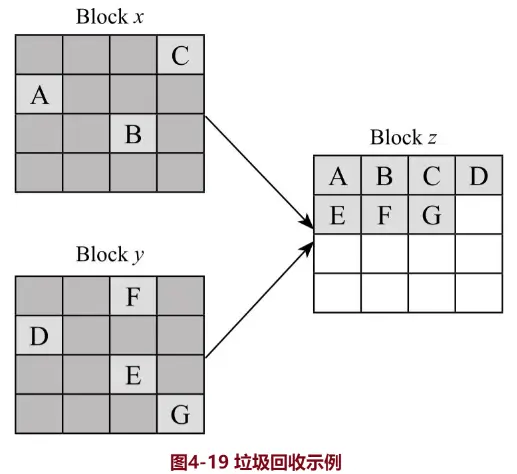

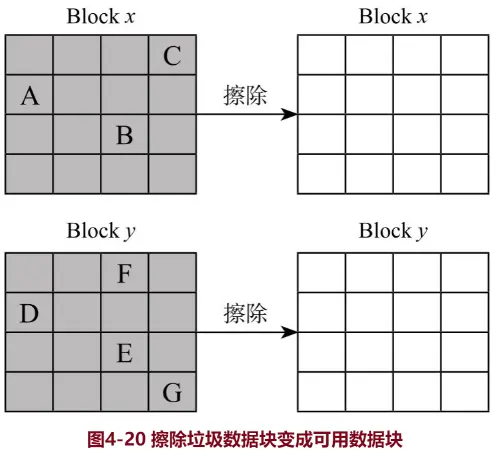

垃圾回收,就是把某个闪存块上的有效数据(图4-19中浅色方块)读出来,重写,然后把该闪存块擦除,就得到新的可用闪存块了。

图4-19中,Block x上面有效数据为A、B、C, Block y上面有效数据为D、E、F、G,其余方块为无效数据。垃圾回收机制就是先找一个可用Block z,然后把Block x和Block y的有效数据搬移到Block z上面去,这样Block x和Block y上面就没有任何有效数据,可以擦除变成两个可用的闪存块,如图4-20所示。

再回到我们的小小SSD系统中来。

上例中,由于我们是顺序写入,垃圾集中在Block 0上,上面没有任何有效数据,我们把它们擦除就可以腾出新的写入空间,用户就可以把新的数据写入到垃圾回收完成的Block 0上了。从这个例子中我们可以看出:顺序写,即使是闪存

空间写满后的写(Full Drive写),性能也是比较好的,因为垃圾回收可以很快完成(也许只需要一个擦除动作)。

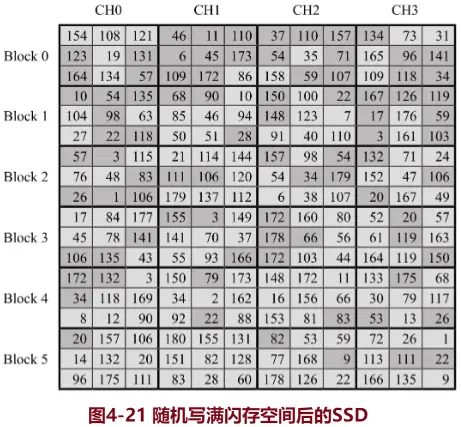

但现实是残酷的:用户写入数据,更多的可能是随机写入数据。下面是一个闪存空间经历随机写满后的样子(见图4-21)。

用户如果继续往SSD上写入数据,那么SSD怎么处理?当然需要做垃圾回收。不过,SSD内部状况比之前看到的复杂多了,垃圾数据分散在每个闪存块上,而不是集中在某几个闪存块上。这个时候,如何挑选需要回收的闪存块呢?答案显而易见,挑垃圾比较多的闪存块来回收,因为有效数据少,要搬移的数据少,这样腾出空闪存块的速度快。

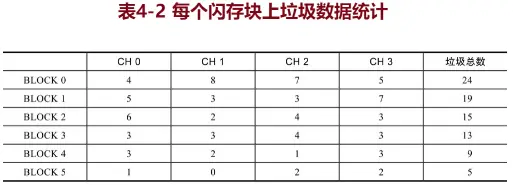

对上面每个闪存块的垃圾数(深色方块)做个统计,如表4-2所示。

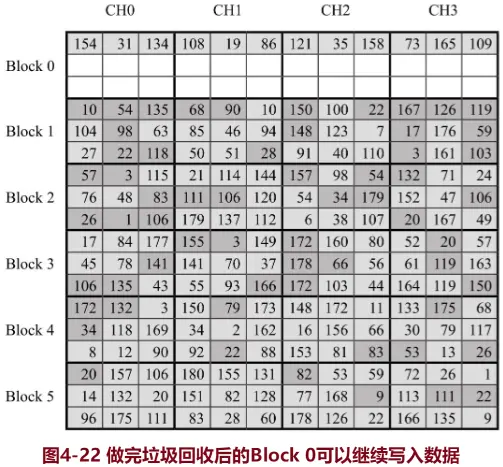

由于是同时往4个通道上写,我们需要每个通道都有一个空闲的闪存块,因此,我们做垃圾回收时,不是回收某个闪存块,而是所有通道上都要挑一个。一般选择每个Die上块号一样的所有闪存块做垃圾回收。上例中,Block 0上的垃圾数量最多(24个深色方块,最多),因此我们挑Block 0作为垃圾回收的闪存块(这里忽略PE Count等因素,只看垃圾数)。回收完毕,我们把之前Block 0上面的有效数据(浅色方块)重新写回到这些闪存块(这里,我们假设回收的有效数据和用户数据写在同一个闪存块,实际上,它们可能是分开写的),如图4-22所示。

这时,有了空闲的空间(白色方块),用户就可以继续写入数据了。

江湖传言:SSD 越写越慢。没错,其实这是有科学依据的:可用闪存空间富裕时,SSD 是无须做 GC 的,因为总有空闲的空间可写。SSD 使用早期,由于没有触发 GC,无须额外的读写,所以速度很快。慢慢地会发现 SSD 变慢了,主要是因为 SSD 需要做 GC。

另外,从上面的例子来看,如果用户顺序写的话,垃圾比较集中,利于SSD做垃圾回收;如果用户是随机写的话,垃圾产生比较分散,SSD 做垃圾回收相对来说就更慢,所以性能没有前者好。因此,SSD 的 GC 性能跟用户写入数据的模式(随机写还是顺序写)也是有关的。

# 6.3.2 写放大

# 6.4 Trim

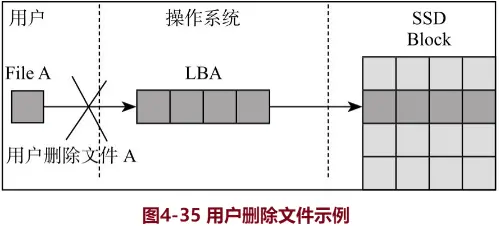

当用户删除掉文件 File A 时,其实它只是切断用户与操作系统的联系,即用户访问不到这些地址空间;而在 SSD 内部,逻辑页与物理页的映射关系还在,文件数据在闪存当中也是有效的,如图4-35所示。

Trim 是一个新增的 ATA 命令(Data Set Management),专为 SSD 而生。当用户删除一个文件时,操作系统(对 Windows 来说,它自 Windows 7 开始支持 Trim)会发 Trim 命令给 SSD,告诉 SSD 该文件对应的数据无效了。一旦 SSD 知道哪些数据无效之后,在做垃圾回收的时候就可以把这些删除掉的数据抛弃掉,不做无谓的数据搬移。这样不仅增强了 SSD 的性能,还延长了 SSD 寿命。

SCSI 里面的同等命令叫 UNMAP, NVMe 里面叫 Deallocate。它们指的都是同一个功能。

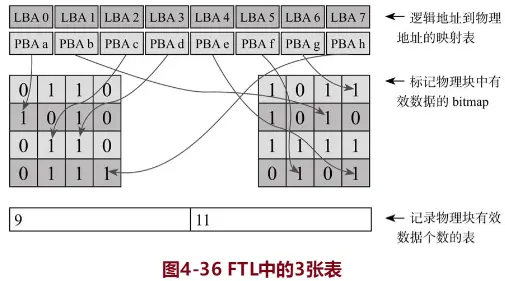

举个例子。主机通过 Trim 命令告诉 SSD:我 0~7 的逻辑页上的数据删除了,你可以把它们当垃圾处理。收到 Trim 命令之前,逻辑页 0~7 有以下映射,它们分别写在物理地址 PBA a~h,如图4-36所示。

一般 FTL 都有这3个表。FTL 映射表记录每个 LBA 对应的物理页位置。Valid Page Bit Map(VPBM)记录每个物理块上哪个页有有效数据,ValidPage Count(VPC)则记录每个物理块上的有效页个数。通常 GC 会使用 VPC 进行排序来回收最少有效页的闪存块;VPBM 则是为了在 GC 时只读有用的数据,也有部分 FTL 会省略这个表。

如图4-36所示,FTL 的映射往往是非常分散的,连续的逻辑页对应地址会在很多不同的闪存块上。SSD 收到 Trim 命令后,为了实现数据删除,固件要按顺序做以下的事情(图4-37中的步骤1~4)。

图4-37中的步骤5~7是 Trim 命令处理后,GC 的处理,它们不是 Trim 命令处理的部分。Trim 命令是不会触发 GC 的。

# 6.5 磨损平衡

磨损平衡,就是让 SSD 中的每个闪存块的磨损(擦除)都保持均衡。

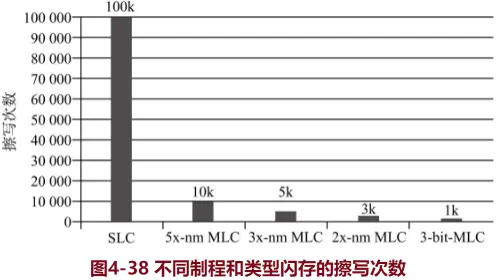

一个闪存块寿命有多长呢?如图4-38所示。

- 冷数据(Cold Data): 所谓冷数据,就是用户不经常更新的数据,比如用户写入 SSD 的操作系统数据、只读文件数据、小电影等;

- 热数据(HotData): 热数据就是用户更新频繁的数据。数据的频繁更新,会在 SSD 内部产生很多垃圾数据(新的数据写入导致老数据失效)。

- 年老的(Old)块:: 擦写次数比较多的闪存块;

- 年轻的(Young)块: 擦写次数比较少的闪存块

SSD 很容易区分年老的块和年轻的块,看它们的 EC(Erase Count,擦除次数)就可以了,大的就是老的,小的就是年轻的。

SSD 一般有动态磨损平衡(Dynamic WL)和静态磨损平衡(Static WL)两种算法。

- 动态磨损平衡: 动态磨损平衡算法的基本思想是把热数据写到年轻的块上,即在拿一个新的闪存块用来写的时候,挑选擦写次数小的;

- 静态磨损平衡: 静态磨损平衡算法基本思想是把冷数据写到年老的块上,即把冷数据搬到擦写次数比较多的闪存块上。

冷数据由于不经常更新,它写在一个或者几个闪存块上后,基本保持不动,这样,这些闪存块的擦写次数就不会增加;相反,对别的闪存块,由于经常拿来写入用户数据,擦写次数是一直增长的。这样就导致闪存块的擦写不均衡。因此,固件需要做静态磨损平衡。

固件具体做静态磨损平衡的时候,一般使用GC机制来做,只不过它挑选源闪存块时,不是挑选有效数据最小的闪存块,而是挑选冷数据所在的闪存块。

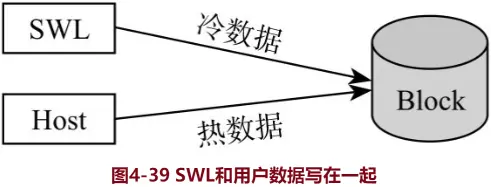

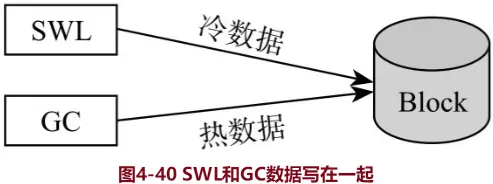

静态磨损平衡可能导致冷数据和热数据混在同一个闪存块上,即冷数据可能跟用户刚写入的数据混在一起,或者冷数据和GC的数据写在一起,或者三者写在一起。

1)SWL 数据和用户数据混在一起写在同一个闪存块上,如图4-39所示。

2)SWL 数据和 GC 数据混在一起写在同一个闪存块上,如图4-40所示。

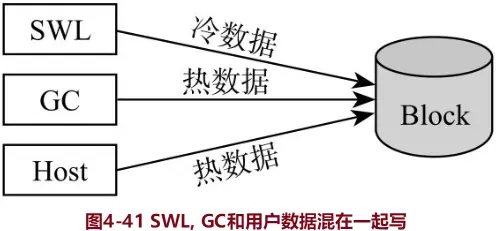

3)三者全都混在一起写在同一个闪存块上,如图4-41所示。

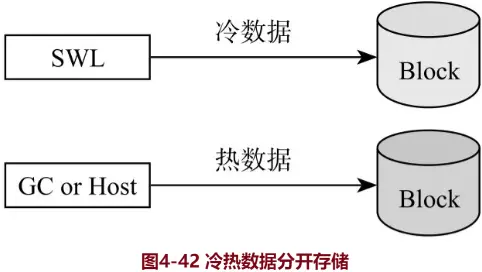

解决办法如图4-42所示,做静态磨损平衡的时候,用专门的闪存块来放冷数据,即不与用户或者 GC 写入同一个闪存块。这样冷数据就单独写在某些闪存块上,它们一般不会挑选为 GC 的源闪存块,也就避免了这些冷数据的频繁搬移。它只有在下一次需要做静态磨损平衡的时候,才会从一个闪存块搬到另外一个闪存块。

不同的 SSD 有不同的静态磨损平衡做法。如果不在乎写放大(EC预算够大,不差钱),也不在乎冷数据搬移导致的性能下降,那么冷热数据混在一起就一起,毕竟实现简单(不需要另外管理静态磨损平衡的闪存块);相反,如果对写放大比较敏感的话,那么最好还是冷热数据分开。

# 6.6 掉电恢复

掉电分两种,一种是正常掉电,另一种是异常掉电。

正常掉电。

在掉电前,主机会通过命令通知 SSD,比如 SATA 中的 IdleImmediately, SSD 收到该命令后,主要会做以下事情:

- 把 buffer 中缓存的用户数据刷入闪存。

- 把映射表刷入闪存。

- 把闪存的块信息写入闪存(比如当前写的是哪个闪存块,以及写到该闪存块的哪个位置,哪些闪存块已经写过,哪些闪存块又是无效的等)。

- 把 SSD 其他信息写入闪存。

主机等 SSD 处理完以上事情后,才会真正停止对 SSD 的供电。正常掉电不会导致数据的丢失

异常掉电

就是 SSD 在没有收到主机的掉电通知时就被断电;或者收到主机的掉电通知,但还没有来得及处理上面提到的那些事情,就被断电了。

- 异常掉电可能会导致数据的丢失,比如缓存在 SSD 中的数据来不及写到闪存,掉电导致这部分数据丢失。

- 还有,根据闪存特性,如果掉电发生在写 MLC 的 Upperpage,会导致其对应的 Lower Page 数据遭到破坏,也就是意味着之前写入闪存的数据也可能由于异常掉电导致丢失。

- 异常掉电恢复的目的一方面是尽可能恢复用户数据,把损失减到最低;另一方面是让 SSD 经历异常掉电后还能正常工作。

一个 SSD,除了数据掉电不丢失的闪存,还需要有掉电数据丢失的 RAM、SRAM 或者 DRAM。

闪存的作用是存储数据,而 RAM 的作用主要是 SSD 工作时用以缓存用户数据和存放映射表(Map Table,逻辑地址映射闪存物理地址)。所以一旦掉电,RAM 的数据就会丢失。

为防止异常掉电导致的数据丢失,一个简单的设计就是在 SSD 上加电容,SSD 一旦检测到掉电,就让电容开始放电,然后把 RAM 中的数据刷到闪存上面去,从而避免数据丢失。

还有一个比较前卫的想法,就是把 RAM 这种 Volatile(掉电数据丢失)的东西,用 Non-Volatile(掉电数据不丢失)的东西来替代,但要求这种 Non-Volatile 的东西性能上接近 RAM。这样,整个 SSD 都是 Non-Volatile 的了。Intel 和 Micron 合作开发的 3D XPoint,可作为一个选择。3D XPoint 兼有闪存掉电数据不丢失和内存快速访问的特点。

# 6.7 坏块管理

# 4.7.1 坏块来源

- 出厂坏块(Factory Bad Block):闪存从工厂出来,就或多或少的有一些坏块。

- 增长坏块(Grown Bad Block):随着闪存的使用,一些初期好块也会因为擦写磨损变成坏块。

# 4.7.2 坏块鉴别

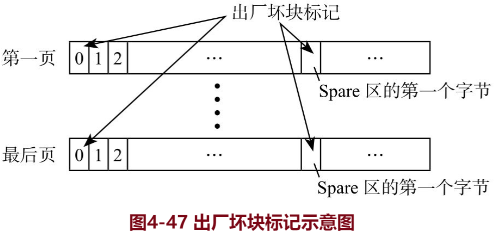

刚出厂的闪存一般都会被擦除,里面的数据全是0xFF,而坏块会被的打上不同的标记。例如:TOSHIBA某型号闪存,如图4-47 所示:

它会在出厂坏块的第一个闪存页和最后一个闪存页的数据区第一个字节和Spare区第一个字节写上一个非0xFF的值。

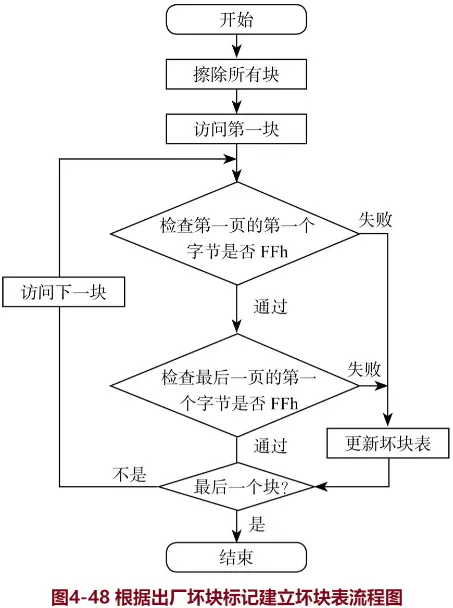

用户使用闪存时应先按照闪存文档扫描所有闪存块剔除坏块,建立一张坏块表。TOSHIBA建议按照下面的流程来建立坏块表(见图4-48)。

部分闪存厂商会把坏块信息存储在闪存内部某个地方(掉电不丢失),用户建立坏块时只需读取闪存的那个特定区域。例如:Micron,它的闪存内部有个叫 OTP(One Time Programming)的区域,出厂坏块信息可以存在里面。

对增长坏块而言,它的出现会通过读写擦等操作反映出来。比如读到 UECC(Uncorrectable Error Correction Code,数据没有办法通过 ECC 纠错恢复)、擦除失败、写失败,这都是一个坏块出现的症状。用户应该把这些坏块加入坏块表,不再使用。

# 4.7.3 坏块管理策略

一般有两种策略管理坏块,一是略过(Skip)策略,二是替换(Replace)策略。

略过策略

用户根据建立的坏块表,在写闪存的时候,一旦遇到坏块就跨过它,写下一个Block。

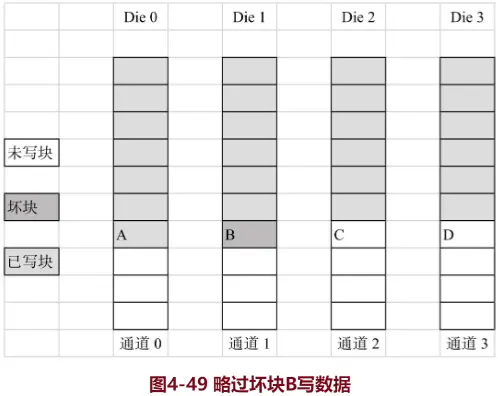

SSD 的存储空间是闪存阵列,一般有几个并行通道,每个通道上连接了若干个闪存。以图4-49为例,该 SSD 有四个通道,每个通道上挂了一个闪存 Die。SSD 向四个 Die 依次写入。假设 Die 1上有个 Block B 是坏块,若固件采取坏块略过策略,则写完 Block A 时,接下来便会跨过 Block B 写到 Die 2 的 Block C 上面去。

替换机制

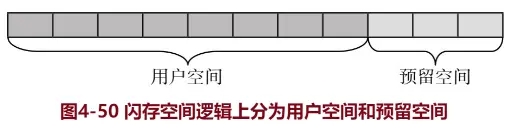

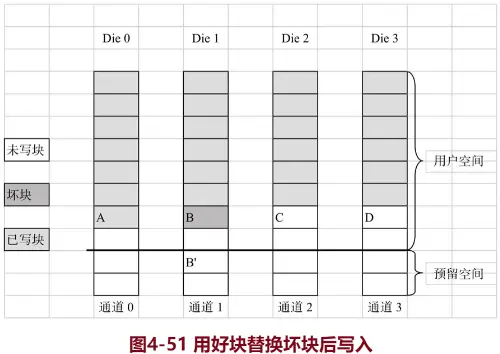

当某个 Die 上发现坏块时,它会被该 Die 上的某个好块替换。用户在写数据的时候,不是跨过这个 Die,而是写到替换块上面去。此策略需额外保留一部分好的闪存块,用于替换用户空间的坏块。整个 Die 上闪存块就划分为两个区域:用户空间和预留空间,如图4-50所示。

还是以上面的情况为例:用户写入数据时,当碰到坏块B,它不会略过Die 1不写,而是写入到Block B的替换者Block B′上面去。

采用替换策略,SSD 内部需维护一张重映射表(Remap Table):坏块到替换块的映射,比如图4-51的 B→B′。当 SSD 需要访问 Block B 时,它需要查找重映射表,实际访问的物理 Block 应该是 B′。

两者策略优劣:

- 略过策略: 性能不稳定,Die 的并行度在1和4给 Die 之间;

- 替换策略: 性能稳定,Die 的并行度总是4个 Die;有木桶效应,如果某个 Die 质量较差,则整个 SSD 可用的闪存块则受限于那个坏的 Die。

# 4.8 SLC cache

SLC、MLC 和 TLC 在性能和寿命上的直观比较,如表4-10所示。

SLC 有速度优势,因此拿它在做 CaChe 使用可让 SSD具有更好的突发性能。

这里所说的 SLC Cache,不是说单独拿 SLC 闪存来做 Cache,而是把 MLC 或者 TLC 里面的一些闪存块配置成 SLC 模式来访问,而这个特性一般的 MLC 或者 TLC 都是支持的

使用 SLC Cache 的出发点,主要有以下几点:

性能考虑: SLC 性能好,用户数据写到 SLC 比直接写到 MLC 或者 TLC 上快很多。

**防止 Lower Page 数据被带坏: **用户数据写到 SLC,不存在写 Upper Page 或者 Extra Page 带坏 Lower Page 数据的可能。

解决闪存的缺陷: 比如有些 MLC 或者 TLC 的闪存块,如果没有写满,然后去读的话,可能会读到 ECC 错误,而对 SLC 模式下的闪存块,就没有这个问题。

更多的数据写入量: SLC 更耐写。

SLC Cache 写入策略有:

强制 SLC 写入: 用户写入数据时,必须先写入到 SLC 闪存块,然后通过 GC 搬到 MLC 或者 TLC 闪存块;能保护 Lower Page 数据,但是因为一方面要把 SLC 的数据搬到 MLC 或者 TLC ,以腾出 SLC 空间供新用户数据的写入,同时又要把用户数据写入到 SLC,性能肯定比只写 MLC 或者 TLC 慢。

非强制 SLC 写入: 用户写入数据时,如果有 SLC 闪存块,则写入到 SLC 闪存块,否则直接写到 MLC 或者 TLC 闪存块。不能保护 Lower Page 数据,但有更好的后期写入性能,因为在 SLC 闪存块耗尽的情况下,用户数据直接写入到 MLC 或者 TLC。

强制写入 SLC 策略, SLC 数据最后都要搬到 MLC 或者 TLC,所以还是存在直接写 MLC 或者 TLC 的事实,也就是还是存在 Lower Page 数据被带坏的可能。是的,没错,做 GC(数据搬移)是有这个问题。但是,如果我们在目标闪存块没有被写满前,不把源闪存块擦除,这样即使 Lower Page 数据被带坏,它还是能通过读源闪存块恢复数据,是不是?

SLC Cache 办法:

静态 SLC Cache: 拿出一些 Block 专门用做 SLC Cache。

动态SLC Cache: 所有的 MLC 和 TLC 都有可能挑来当 SLC Cache,SLC 和 TLC 不分家;

两者混合: 即既有专门的 SLC 闪存块,还能把其他通用闪存块拿来当 SLC Cache。

# 4.9 RD& DR

RD 指的是 Read Disturb, DR 指的是 Data Retention。两者都能导致数据丢失,但原理和固件处理方式都不一样。

RD

每次读一个闪存页都会在其他字线(Wordline)上加较高的电压以保证晶体管导通。长此以往,由于电子进入浮栅极过多,从而导致比特翻转:1→0。当出错比特数超出 ECC 的纠错能力时,数据就会丢失。这就是 RD 的原理。

如果我们能保证某个闪存块读的次数低于某个阈值,在比特发生翻转之前(或者翻转的比特低于某个值时),就对这个闪存块上的数据进行一次刷新:把闪存块上的数据搬到别的闪存块上(或者先搬到别的闪存块上,然后擦除原闪存块后,再复制回来),防患于未然,这样就能解决 RD 导致数据丢失的问题。

因此,FTL 应该有记录每个闪存块读次数的一张表:每读一次该闪存块,对应的读次数加1。当 FW 检测到某个闪存块读的次数超过某个阈值,就刷新该闪存块。当数据写到新的闪存块后,读次数归零,一切重新开始。每个闪存块的读次数,掉电时应该保存到闪存上,重新上电时,再加载它们。

事实上,当某个闪存块上的读次数超出阈值时,上面的数据翻转可能并没有超过很多(可设阈值),这种情况就没有必要立刻刷新。毕竟,刷新代来的读数据和写数据,需要耗时间和擦写次数,对性能和闪存寿命有影响。因此,有些 FTL 为避免“过”刷新,可能会在读次数超过阈值后,先检测比特翻转数,然后决定是否真正需要刷新,如果不需要立刻刷新,会重新设置一个更大的阈值,待下次读的次数达到新阈值后,重复之前的操作。

其实,RD 与闪存的年龄有关:年龄越大(PE 越大),对 RD 的免疫力越低。因此,对阈值的设定,采用动态的才是合理的,即对不同的 PE,读阈值应该不同。具体来说,PE 越大,读阈值应该越小。

关于刷新动作,有Block(阻塞)和Non-block(非阻塞)两种处理方式。所谓阻塞方式,就是固件把其他事情都放在一边,专门处理闪存块的刷新;所谓非阻塞方式,就是闪存块的刷新与其他操作同时进行(Interleave操作)。前者处理方式劣势明显,那就是带来很长的命令时延:在处理闪存块的刷新的时候,就不能执行读写操作,导致读写推后。随着闪存块尺寸的增大,这种处理方式的劣势越发凸显。所以,现在的FTL一般都采用非阻塞的刷新处理方式。

DR

绝缘氧化层把存储在浮栅极的电子关在里面,但是,随着时间的推移,还是有电子从里面跑出来。当跑出来的电子达到一定数量时,就会使存储单元的比特发生翻转:0→1(注意,RD 是使1翻转为0),当出错比特数超出 ECC 的纠错能力,数据就丢失。这就能解释为什么你的固态硬盘如果很长时间不用,可能就启动不了,或者启动很慢(固件需要处理由于DR引起的数据错误)的现象了。

问题来了,为什么 SSD 长久不用数据就会丢失,而经常使用却不会呢?原因是 FW 或者 FTL 立功了。针对 DR 这个问题,稍微好一点的 SSD, FTL 都会有相应的处理。怎么处理呢?FTL 在 SSD 上电或者平时运行时,每隔一段时间对闪存空间进行扫描,当发现比特翻转超出一定阈值时,跟 RD 处理一样,进行数据刷新,这样就能避免数据彻底丢失。SSD 如果常年不上电,FTL 根本就没有机会执行这些操作,只能眼睁睁地看着电子流失。

# 4.10 Host Based FTL

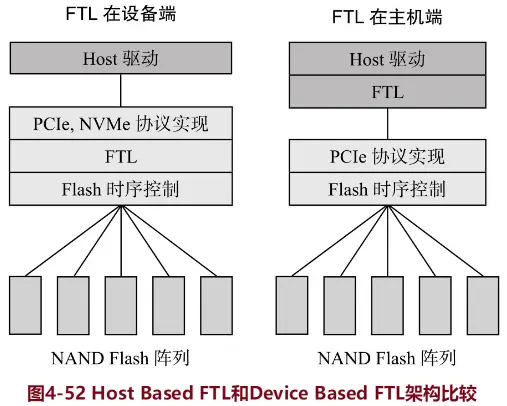

按照 FTL 放在哪里划分,SSD 有 Host Based FTL 和 Device Based FTL 两种模式。

- Host Based FTL: 放在主机驱动程序中,也有一些企业级 SSD 采用了 Host Based FTL,像垃圾回收、磨损平衡、坏块管理等都放在主机驱动程序中完成,这种模式的优点是可以实现差异化。

- Device Based FTL: 放在 SSD 主控内部,大部分企业级 SSD 和几乎全部消费级 SSD 都是 Device Based,SSD主控芯片做了包括FTL在内的所有控制工作。

# 4.10.1 Device Based FTL 的不足

图4-52所示是两种模式的架构对比。看得出来,从逻辑上来说,一个完整的 Device Based SSD 系统可以分为三块:

- 主机驱动:为应用程序提供读写接口;和板载控制器通过 NVMe 等协议进行交互,完成应用程序的读写命令。

- 板载控制器:

- 通过SATA、NVMe等协议,接收主机发送的命令并执行。

- 管理SSD,实现FTL垃圾回收、磨损平衡等算法。

- 控制和实现闪存时序。

- 闪存阵列:存储介质。

总体来说,Device Based 存在以下缺点:

- FTL 架构通用,不能针对具体应用做定制化。

- 控制器芯片功能复杂,设计难度大,研发成本高。

- 闪存更新很快,一般每年闪存厂商都会推出新一代产品,有新的使用特性,需要控制器芯片做出修改,但是芯片改版成本很高。

- 企业级应用需要高性能、大容量,通用控制器芯片支持的最大性能和容量有限制。

- 企业级市场需求多种多样,有些需求需要控制器提供特殊功能支持,这些是通用 SSD 主控芯片无法提供的。

为了解决这些问题,有些企业级 SSD 采用了 Host Based 方案。也有一些大型互联网公司,例如 Google、Microsoft,还有百度等,自己研发 Host BasedSSD,针对自己的存储架构,开发驱动程序和控制器逻辑。

# 4.10.2 Host Based FTL 架构

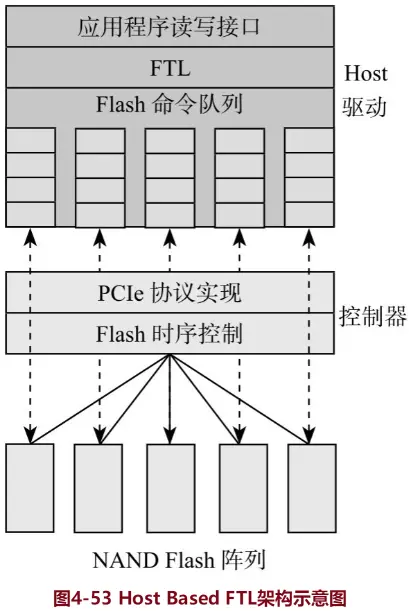

Host Based SSD 一般的模式是把闪存的读写接口直接开放给驱动程序,这样驱动程序就能自行管理闪存内部资源。控制器大都采用可编程逻辑器件 FPGA,功能比较简单,主要实现 ECC 纠错和闪存时序控制。

如图4-53所示,主机驱动直接管理闪存阵列,控制器只是起到 ECC 纠错算法和物理协议转换的作用。

# 4.10.3 百度的软件定义闪存 SDF

SDF 主要的特点有:

- 没有垃圾回收。SDF 的使用者使用闪存块大小的整数倍为单位来写数据(比如8 MB),所以每个闪存块里面不会有垃圾,或者整体都是垃圾,写之前直接擦除就可以了。这样的好处有:

- SSD 内部不用做垃圾回收,读写带宽得到提高。

- 不需要预留空间,释放出20%的额外空间。

- 没有内部搬移数据产生的写操作,闪存没有了写放大,寿命延长。

- 没有闪存级 RAID。SSD 内部其实是闪存阵列,所以为了数据安全性,很多企业级 SSD 会用闪存组成 RAID 组,用一块或几块闪存保存 RAID 数据。但是互联网公司的数据一般都有3个备份,所以不担心 SSD 内部数据丢失,因此,RAID 是没有必要的。

- FPGA 作为控制芯片,功能很少:ECC、坏块管理、地址转换、动态磨损平衡。Virtex-5 FPGA 实现了 PCIe 接口和DMA, Spartan FPGA 则是闪存控制芯片。

- SSD 内部每个通道都向用户开放,由用户选择写哪个通道。

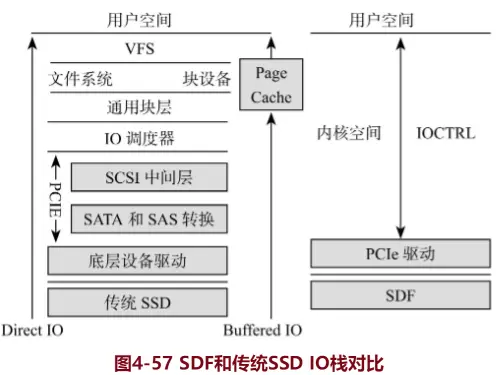

- 软件接口层非常简单,相比传统的 Linux 存储堆栈,省略了文件系统、块设备、IO调度、SATA 协议等,用户直接通过 IOCTRL(设备驱动程序中对设备的 I/O 通道进行管理的函数)来发同步的写命令到PCIe驱动,如图4-57所示。软件延迟从12μs缩减到2~4μs,这个时间只是花在 PCIe 中断处理上。